국산화, 국내 장비사 성장의 1 등 공신

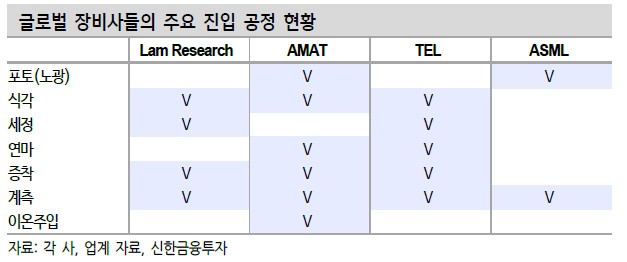

반도체 장비는 글로벌 상위 장비사인 AMAT, ASML, Lam Research, TEL 등이 시장 점유율 약 60% 이상을 차지하고 있는 상황이다. 국내 장비사들은 국내 반도체 산업의 성장과 함께 후발 주자 입장에서 진입을 노력해왔다

그럼에도 여전히 국내 장비 국산화율은 20%에 못 미치는 수준으로수준으로, 국산화 영역은 많이 남아있다.

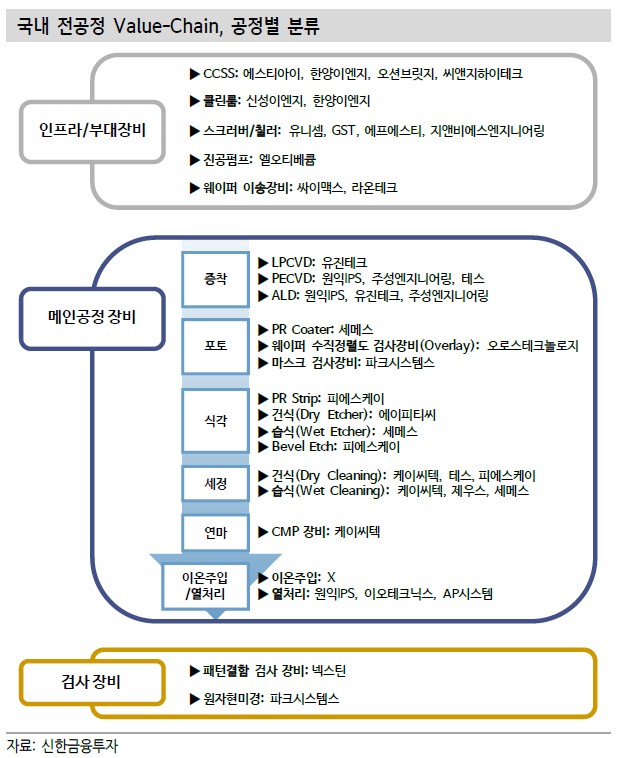

공정별/적용처별 국산화 현황

공정별로 보면, 인프라/부대장비 – 증착 장비 – 세정 ㆍ연마 장비 – 식각 장비순으로 국산화가 많이 진행됐다.

기술적 진입장벽, 공정 난이도가 높을수록 국산화 진행이 상대적으로 더디다. 인프라 설비나 부대장비(스크러버, 칠러, 진공펌프 등)의 경우 국산화율은 100%에 가깝다.

세정과 식각 장비는 각각 30%, 10%를 하회할 정도로 국산화율이 낮고, 단기간 내 비약적인 국산화율 상승을 기대하기

어려운 상황이다.

현 시점에서 국산화 모멘텀이 강한 분야는 증착 장비다. 가장 활발하게, 가시적으로 국산화가 진행 중이다.

적용처별로 볼 경우, 비메모리에 대한 국산화율이 낮다. 가장 국산화율이 높은 인프라 장비들도 비메모리 분야 는 일부 국산화가 필요한 부분이 남아있다.

▶증착장비

현재 증착 장비군에서 국산화가 가장 활발히 진행되는 부분은 배치(Batch Type) 장비다. 3D 구조화, 적층수 고단화가 진행될수록 배치 장비의 중요성이 높아진다. 배치 장비는 일본 장비사들이 강점을 가지고 있던 분야다. 일본의 TEL, Kokusai 등이 기존에 독점하고 있던 공정들에 대한 국산화가 활발히 진행 중이다.

▶세정장비

비메모리를 중심으로 국산화가 진행되고 있다. 메모리에서도 국내 장비사들의 점유율은 약 30% 수준으로 국산화가 더 필요하나, 비메모리는 이보다 낮은 수준이다. 삼성전자의 비메모리 투자 확대와 맞물려 국산화율 증가가 예상된다.

▶식각 장비

식각장비의 경우, 소재별로 폴리와 메탈 계열에 대한 국산화가 일부 진행됐으며, 여전히 핵심 공정에 대한 국산화는 미미한 상황으로 5% 미만 수준인 것으로 추정된다. 그 외에 범식각 장비로 분류될 수 있는 PR Strip 장비의 경우 메모리 내에서는 대부분 국산화가 완료됐으며, 비메모리에 대한 국산화가 진행 중이다.

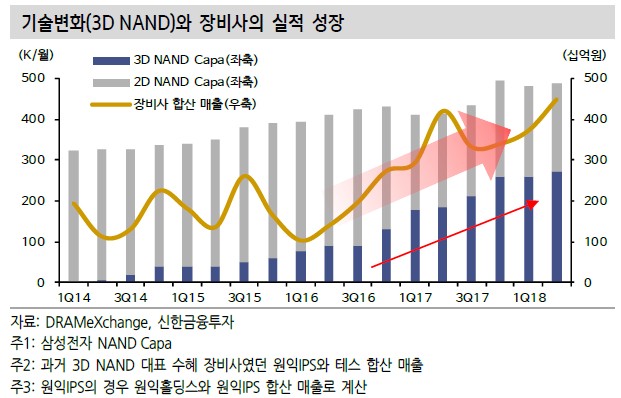

국산화 확대는 기술변화와 함께

앞으로 진행될 국산화에 대한 힌트는 기술변화로부터 얻을 수 있다. 과거 국내 장비사들의 국산화 진척도가 크게 향상되는 시기는 기술변화와 관계가 있었다.

대표적인 사례가 3D NAND 도입이다. 해당 기간(2013년~)에 인프라/부대 장비 및 메인 장비 회사들은 삼성전자와 SK하이닉스 국산화율이 크게 확대됐다.

주요 기술변화 진화 에 따른 공정별 영향

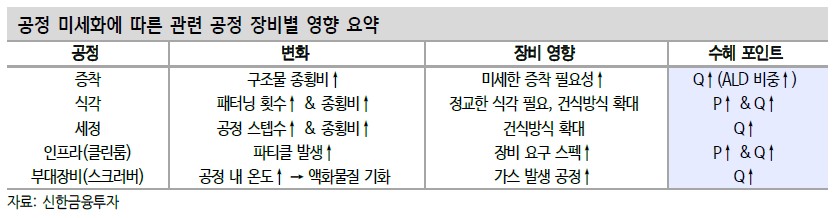

1. 공정미세화

반도체 생산업체들의 끝나지 않는 숙제는 집적도 향상이다. 웨이퍼 면적당 많은 칩을 생산하는 것이 중요하다. 이를 위 해 회로 선폭 줄이기를 위한 노력이 지속된다.

▶장비 영향

미세화가 진행될수록 공정 스텝수는 증가하게 된다. 1z 1a 1b로 넘어갈수록 동일 캐파당 필요 한 장비대수가 증가 한다.

또한 신규 팹에 선단 공정을 적용하면 이전 팹들은 보완투자(Migration)가 진행된다. 보완투자 를 진행하는 팹들 역시

동일한 효과가 발생하면서 필요 장비대수의 증가가 발생한다.

- 증착 장비

공정 미세화 로 DRAM의 캐패시터 등 구조물의 종횡비(Aspect Ratio)가 커진다. 종횡비가 커질수록 미세한 증착이 요구된다. 절연막 두께를 1나노 이하 수준으로 얇게 만들어야 하는데, 이를 위해서 ALD 방식의 증착이 필요하다.

- 식각장비

패턴이 미세화되면서 멀티 패터닝(2회 이상)이 요구된다. 이전 대비 식각 공정의 차지 비중이 증가함에 따라 장비 사용 대수도 증가한다. 또한 정교한 식각을 위해 습식(Wet) 식각보다 건식(Dry) 식각 위주로 전환됐다. 습식 식각은 가로, 세로 방향 모두에 영향을 끼치기 때문에 깊이 뿐 아니라 넓이에도 영향을 미친다. 이는 얇고 깊게 파야하는 미세화 측면에서 적합하지 않다. 반면 건식 식각은 한 방향으로만 영향을 미치기 때문에 습식 방식보다 적합하다.

- 세정장비

멀티 패터닝으로 식각 공정 스텝수가 증가하면, 세정 공정의 스텝수 증가로 이어진다. 더불어 식각과 마찬가지로 습식(화학 용액 사용) 보다 건식(플라즈마 등) 방식으로 전환이 확대됐다. 구조물의 종횡비가 높아 질수록 화학용액이 깊은 곳까지 닿기 어려워진다. 건식 세정이 유리한 상황이 전개된다.

- 클린룸장비

공정이 미세화 될수록, 공정 중 파티클이 많이 발생하게 된다. 클린룸 장비에 대한 요구 스펙과 대수가 모두 증가한다. 스펙 증가는 ASP 상승효과로 이어진다.

- 스크러버장비

공정 내 발생 온도가 상승 한다. 기존 액화 물질이 기화하면서 유해 가스 발생량이 증가한다. 가스를 정화시키는 장비가 스크러버다. 스크러버가 필요한 공정이 늘어나고 있다. 더불어 ESG 트렌드 확대에 따른 친환경 방식(플라즈마 등)의 장비 수요가 지속적으로 확대될 것으로 예상된다. 이미 주요 생산업체 들은 에칭 공정 내에 플라즈마 스크러버 채택을 확대시키고 있다.

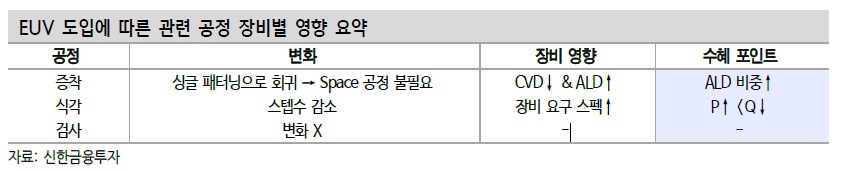

2. EUV 적용 확대

포토 공정은 빛을 이용해 웨이퍼에 회로 패턴을 그려넣는 작업이다. 웨이퍼에 회로를 그리기 위한 식각 공정 이전에, 식각할 부분에 대한 밑그림을 그려놓는 단계다. 최근 고성능 반도체 수요가 증가하면서, 생산업체들의 회로 선폭을 줄이기 위한 노력이 지속되고 있다.

이를 위해 기존 파장인 DUV(심자외선, ArF) EUV(극자외선)로의 전환은 필수적이다. ArF(불화아르곤) 대비 EUV는 파장이 짧아 14배 가량 더 세밀하게 회로를 그릴 수 있다.

글로벌 유일 EUV 장비 제조사인 ASML에 따르면, 2020년 EUV 장비 보급 비중은 파운드리 90%, 메모리 10%였다. 주요 반도체 생산업체들은 비메모리에 이어 메모리에서도 EUV 적용을 확대하고 있어, 메모리 적용 비중의 점진적 확대가

예상된다.

▶ 장비 영향

스텝수 감소(멀티 패터닝 → 싱글 패터닝)에 따른 영향이 발생한다. 기존 포토 공정시에는 미세화 될수록 회로를 그리는 과정에서 여러 번(2회 이상)의 작업이 필요했다. EUV는 DUV 보다 정밀도가 높기 때문에 미세 회로를 그려도 한 번의

패터닝만으로 가능하다. 생산업체들은 EUV 장비를 통해 비용 절감이 가능하다.

- 증착장비

싱글 패터닝으로 바뀌면서 스텝수가 감소하면 CVD 증착 장비에 대한 수요가 줄어들 수 있다. Spacer 공정이 불필요해지기 때문이다. 싱글 패터닝에서는 Spacer가 필요하지 않기 때문에 CVD에 대한 수요는 감소한다. 다만, 원래 Spacer 증착에 ALD는 사용되지 않았기 때문에 EUV 도입에 따른 감소는 없다. 오히려 미세화로 인해 ALD는 늘어나는 공정이 추가된다

- 식각장비

증착과 마찬가지로 싱글 패터닝에 따라 스텝수가 감소하면 장비 대수는 감소하는 효과가 발생할 수 있다. 장비에 대한 요구 스펙 증가로, ASP 상승 효과가 있겠으나 공정 스텝수 감소의 영향이 좀 더 클 것으로 전망된다.

- 검사장비

포토 공정 검사 장비는 대표적으로 Overlay 장비가 있다. 웨이퍼의 상하부 수직 정렬도를 계측하는 장비로, 해당 장비는 EUV 적용 전과 후에 역할이 달라지지 않는다. 큰 영향을 받지 않을 것으로 판단된다.

3. 3D 구조

삼성전자는 2013년 최초로 3차원 V-NAND를 양산했다. 공정 기술이 10나노 대역으로 진입 한 이후 셀 간 간격이 좁아지고 간섭현상이 심해지면서, 추가적으로 트랜지스터 크기를 줄이기 어려워지는 등 물리적 한계 에 도달했다. 이를 극복

하기 위해 생산업체들이 고안한 방법이 Vertical(수직 적층) 구조 도입 이었다.

그러나 단수가 높아질수록 홀(Hole)의 깊이가 깊어짐에 따라 식각 공정의 난이도가 증가한다. 균일하고 올곧게 에칭하는(뚫는) 것이 중요한데, 깊이가 깊어질수록 어렵다. 아래쪽 깊은 층들에서 위쪽 얕은 층들과 달리 에칭이 불량하게 되는되는(울퉁불퉁) 등의 문제점이 발견됐다.

삼성전자는 128단까지 한번에 완벽하게 에칭할 수 있었고, SK하이닉스 72단부터 에칭에 어려움을 겪었다. 이를 해결하기 위해 생산업체들은 Double Stack 방식을 적용했다.

Double Stack 방식은 한번에 에칭이 가능한 만큼 작업 후 2개를 적층시키는 방식이다. 예를 들어들어, 10단 1개와

20단 1개를 붙이면 30단 1개를 만들 수 있다. 삼성전자는 176단부터 Double Stack을 적용할 예정이다.

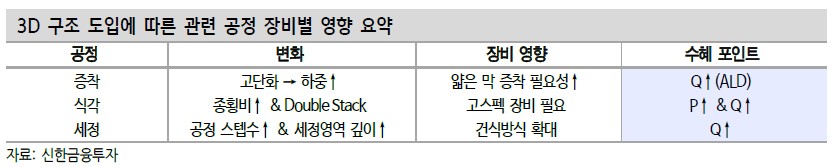

▶장비 영향

- 증착장비

고단화 될수록 하중이 커지면서 하부층이 휘어질 수 있다. 또한 두께가 높아 위아래 높이가 높아지면 전력 소모 역시 크게 발생한다. 그래서 막의 두께를 얇게하고 전체 높이를 최소화할 필요가 있다. 얇고 균일하게 증착할 수 있는 ALD 사용 비중이 늘게된다.

- 식각장비

적층수 고단화로 인한 수혜가 가장 큰 공정이다. NAND 홀(Hole)의 종횡비가 커진다. 에칭해야 하는 깊이가 깊어질수록 고스펙(ASP↑) 장비가 필요하다. 또한 Double Stack으로 할 경우, 홀(Hole)에 대한 식각은 2번 필요하다.

- 세정장비

고단화 과정에서 큰 수혜가 확인된다. 한 층의 공정이 끝날 때마다 세정 작업이 필요하다. 단층 수가 확대될수록 세정 공정에 대한 수요가 증가한다. 더불어 홀(Hole)의 종횡비 가 증가하면서 세정 난이도 증가로 습식보다 건식 세정 사용 비중이 증가한다.

'산업분석 > 반도체,디스플레이' 카테고리의 다른 글

| 2022년 PCB 업종의 이슈별 투자 포인트 (0) | 2022.02.23 |

|---|---|

| 디스플레이: OLED Mask 산업 살펴보기 (0) | 2022.02.09 |

| 반도체 장비주에 대한 고민과 해답, 실적변수 (0) | 2022.01.26 |

| 반도체 장비주, 접근법의 변화 (0) | 2022.01.26 |

| [공유] 반도체 밸류체인 (0) | 2022.01.24 |